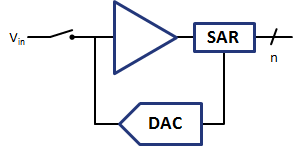

10b 100kSps ultra-low power SAR ADC

Description:

The nSAD_ST65LP_1V2_AD10b100k is a 10b 100kS/s, 8.9 ENOB, ultra-low-power SAR AD converter designed on the ST CMOS 65nm process. It consumes 600nW on silicon, reaching an energy efficiency of 12.5fJ/conversion-step.

Applications:

Ultra-low power sensor interface

Autonomous sensor network nodes

Battery powered systems

Energy harvesting powered systems

Main features:

600nW consumption during operation

Power-down consumption of 10nW

0.037mm² silicon area

20mV/V gain error and 1mV offset typical

55.3dB SNDR

62.6dB SFDR

1.1LSB INL and 2.3LSB DNL

1kHz ERBW

Product brief:

Main characteristics:

ST CMOS 65nm

0.7V supply voltage

10b interface

100kS/s

8.9 ENOB

600nW

ST CMOS 65

Deliverables:

GDS II layout

LEF abstract

CDL netlist

Liberty timings

Verilog description

A full datasheet

An integration note

Status:

Silicon proven

Radiation proven:

No

Automotive grade:

No